ESD

TVS

MOS

LDO

Diode

Sensor

DC-DC

# **Product Specification**

| Domestic Part Number     | IRF9Z24N |

|--------------------------|----------|

| Overseas Part Number     | IRF9Z24N |

| ▶ Equivalent Part Number | IRF9Z24N |

## -60V P-Channel Enhancement Mode MOSFET

### Description

The IRF9Z24N uses advanced trench technology to provide excellent R<sub>DS(ON)</sub>, low gate charge and operation with gate voltages as low as 4.5V. This device is suitable for use as a Battery protection or in other Switching application.

## **Application**

Battery protection

Load switch

Uninterruptible power supply

## **General Features**

$V_{DS} = -60V I_{D} = -20A$

$R_{DS(ON)} < -110 \,\text{m}\Omega$  @  $V_{GS} = -10 \,\text{V}$

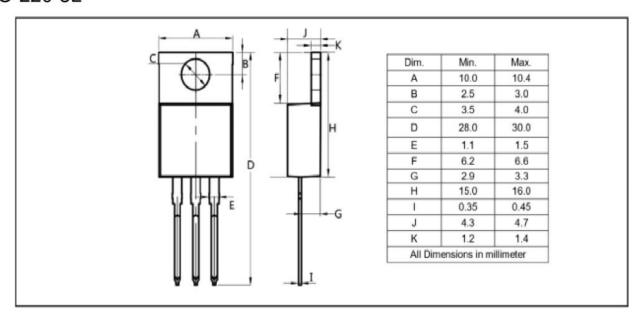

## **TO-220-3L Pin Configuration**

#### Absolute Maximum Ratings (T<sub>C</sub>=25℃unless otherwise noted)

| Parameter                                                | Symbol                           | Limit      | Unit |  |

|----------------------------------------------------------|----------------------------------|------------|------|--|

| Drain-Source Voltage                                     | V <sub>DS</sub>                  | -60        | V    |  |

| Gate-Source Voltage                                      | V <sub>GS</sub>                  | ±20        | V    |  |

| Drain Current-Continuous                                 | lo                               | -20        | Α    |  |

| Drain Current-Continuous(Tc=100 ℃)                       | I <sub>D</sub> (100°C)           | -16        | Α    |  |

| Pulsed Drain Current                                     | Ірм                              | -260       | Α    |  |

| Maximum Power Dissipation                                | PD                               | 1.92       | W    |  |

| Derating factor                                          |                                  | 0.87       | W/°C |  |

| Single pulse avalanche energy (Note 5)                   | Eas                              | 50         | mJ   |  |

| Operating Junction and Storage Temperature Range         | T <sub>J</sub> ,T <sub>STG</sub> | -55 To 175 | °C   |  |

| Thermal Resistance, Junction-to-Case <sup>(Note 2)</sup> | Reuc                             | 65         | °CM  |  |

| Drain-Source Breakdown Voltage   | BV <sub>DSS</sub>   | V <sub>GS</sub> =0V I <sub>D</sub> =-250µA                              | -60  | -     | -    | V  |

|----------------------------------|---------------------|-------------------------------------------------------------------------|------|-------|------|----|

| Zero Gate Voltage Drain Current  | loss                | V <sub>DS</sub> =-60V,V <sub>GS</sub> =0V                               | -    | -     | -1   | μA |

| Gate-Body Leakage Current        | Igss                | V <sub>GS</sub> =±20V,V <sub>DS</sub> =0V                               | -    | -     | ±100 | nA |

| Gate Threshold Voltage           | VGS(th)             | V <sub>DS</sub> =V <sub>GS</sub> ,I <sub>D</sub> =-250μA                | -1.0 | -1.63 | -3.0 | ٧  |

| Drain-Source On-State Resistance | RDS(ON)             | V <sub>GS</sub> =-10V, I <sub>D</sub> =-20A                             | 3.0  | 90    | 110  | mΩ |

| Forward Transconductance         | grs                 | V <sub>DS</sub> =-5V,I <sub>D</sub> =-20A                               | -    | 25    | -    | S  |

| Input Capacitance                | Clss                | V <sub>DS</sub> =-25V,V <sub>GS</sub> =0V,<br>F=1.0MHz                  | -    | 1800  | -    | PF |

| Output Capacitance               | Coss                |                                                                         | -    | 420   | -    | PF |

| Reverse Transfer Capacitance     | Crss                |                                                                         | -    | 145   | -    | PF |

| Turn-on Delay Time               | t <sub>d(on)</sub>  | $V_{DD}$ =-30V, $R_L$ =1.5 $\Omega$ , $V_{GS}$ =-10V, $R_G$ =3 $\Omega$ | -    | 53    | -    | nS |

| Turn-on Rise Time                | tr                  |                                                                         | -    | 19    | -    | nS |

| Turn-Off Delay Time              | t <sub>d(off)</sub> |                                                                         | -    | 221   | -    | nS |

| Turn-Off Fall Time               | tf                  |                                                                         | -    | 61    | -    | nS |

| Total Gate Charge                | Qg                  | V <sub>DS</sub> =-30,I <sub>D</sub> =-20A,<br>V <sub>GS</sub> =-10V     | -    | 46    |      | nC |

| Gate-Source Charge               | Qgs                 |                                                                         | -    | 16    |      | nC |

| Gate-Drain Charge                | Qgd                 |                                                                         | -    | 24    |      | nC |

| Diode Forward Voltage (Note 3)   | Vsp                 | V <sub>GS</sub> =0V,I <sub>S</sub> =-20A                                | -    |       | -1.2 | V  |

| Diode Forward Current (Note 2)   | ls                  |                                                                         | -    | -     | -65  | Α  |

| Reverse Recovery Time            | trr                 | TJ = 25°C, $I_F$ =-20A<br>di/dt = -100A/ $\mu$ s <sup>(Note3)</sup>     | -    | 49    |      | nS |

| Reverse Recovery Charge          | Qrr                 |                                                                         | -    | 71    |      | nC |

| Forward Turn-On Time             | ton                 | Intrinsic turn-on time is negligible (turn-on is dominated by LS+LD)    |      |       |      |    |

#### Notes:

- $\textbf{1.} \ \textbf{Repetitive Rating: Pulse width limited by maximum junction temperature}.$

- 2. Surface Mounted on FR4 Board,  $t \le 10$  sec.

- 3. Pulse Test: Pulse Width  $\leq$  300 $\mu$ s, Duty Cycle  $\leq$  2%.

- 4. Guaranteed by design, not subject to production

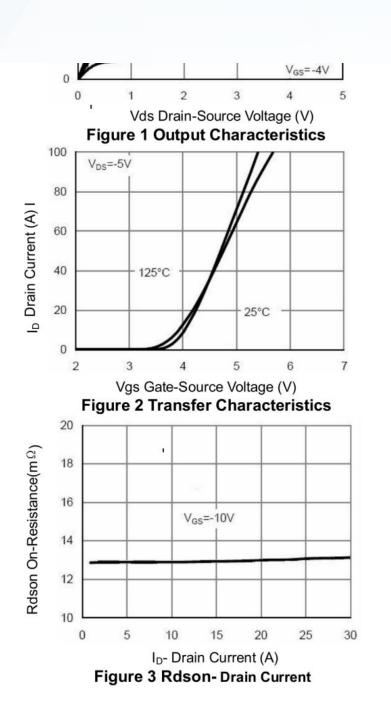

- $\textbf{5.} \ E_{AS} \ condition: \ Tj=25 \ ^{\circ}\text{C}, V_{DD}=-30 \ V, V_{G}=-10 \ V, L=0.5 \ mH, Rg=25 \Omega Typical \ Electrical \ and \ Thermal \ Characteristics \ (Curves)$

O 0.8 0 25 50 75 100 125 150 175 200 T<sub>J</sub>-Junction Temperature(°C) Figure 4 Rdson-Junction Temperature Vgs Gate-Source Voltage (V) V<sub>DS</sub>=-30V I<sub>D</sub>=-20A 8 0 20 30 50 0 10 40 60 70 80 90 Qg Gate Charge (nC) Figure 5 Gate Charge 1.0E+02 1.0E+01 1.0E+00 1.0E-01 125°C

1.0E+02 (Y) 1.0E+01 1.0E+00 1.0E-01 1.0E-02 1.0E-03 1.0E-03 1.0E-04 25°C 25°C 25°C Vsd Source-Drain Voltage (V)

Figure 6 Source-Drain Diode Forward

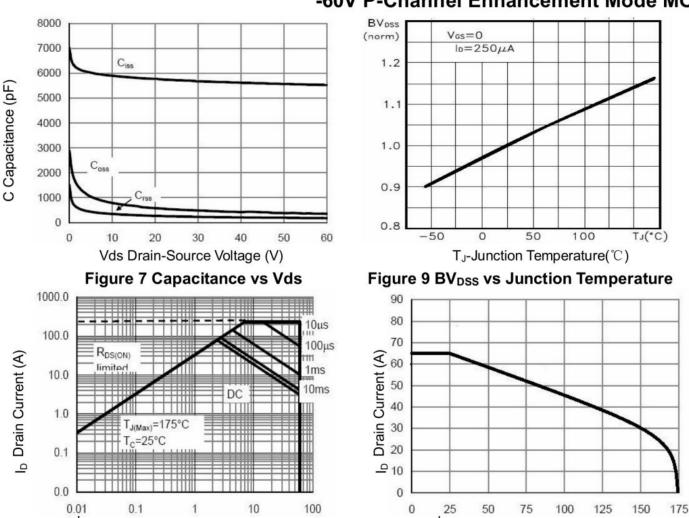

#### -60V P-Channel Enhancement Mode MOSFET

T<sub>J</sub>-Junction Temperature(°C)

Figure 8 Safe Operation Area Figure 10 ID Current Derating vs Junction Temperature

Vds Drain-Source Voltage (V)

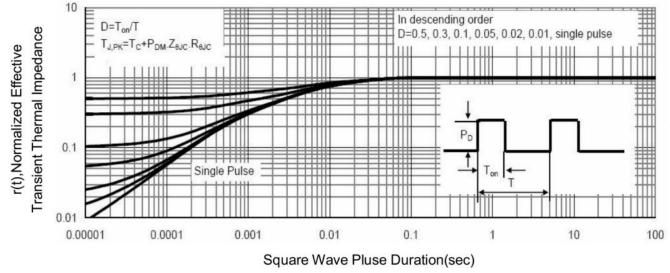

Figure 11 Normalized Maximum Transient Thermal Impedance

### -60V P-Channel Enhancement Mode MOSFET

### TO-220-3L

## Disclaimer

EVVOSEMI ("EVVO") reserves the right to make corrections, enhancements, improvements, and other changes to its products and services at any time, and to discontinue any product or service without notice.

EVVO warrants the performance of its hardware products to the specifications applicable at the time of sale in accordance with its standard warranty. Testing and other quality control techniques are used as deemed necessary by EVVO to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

Customers should obtain and confirm the latest product information and specifications before final design, purchase, or use. EVVO makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does EVVO assume any liability for application assistance or customer product design. EVVO does not warrant or accept any liability for products that are purchased or used for any unintended or unauthorized application.

EVVO products are not authorized for use as critical components in life support devices or systems without the express written approval of EVVOSEMI.

The EVVO logo and EVVOSEMI are trademarks of EVVOSEMI or its subsidiaries in relevant jurisdictions. EVVO reserves the right to make changes without further notice to any products herein.